run <assembly-filename>

[-s, --step-by-step](bool) (run interactively step by step. default: false)

[-d, --data-memory](string) (filename where to save data memory once the program has finished)

[-r, --registers-memory](string) (filename where to save registers memory once the program has finished)

Sample: run samples/sample.txt --step-by-step --data-memory samples/sample.dat --registers-memory samples/sample.reg

If the program is executed using the flag -s or --step-by-step you will be able to see the state of registers and/or data memory at the end of every step executed otherwise if the flag is not provided you will be able to see the final state at the end.

The following menu will be presented:

Press the desired key and then hit [ENTER]...

- (R) to see registers memory

- (D) to see data memory

- (E) to exit and quit

- (*) Any other key to continue

If selected R or D, the data will be displayed in the following format:

0x00 0x04 0x08 0x0C

0x00 0x0000000A 0x0010000A 0x000C0000 0x00000000

0x10 0x000100E8 0x00000008 0x00000012 0x00000087

0x20 0x0000FF00 0x00000000 0x00D00068 0x002000A8

0x30 0x000000E8 0x0000C008 0x00000012 0x00000087

0x40 0x00000012 0x00000000 0x00100000 0x00000000

....

This format applies also if the flags for saving the memory into files by using --data-memory or --registers-memory

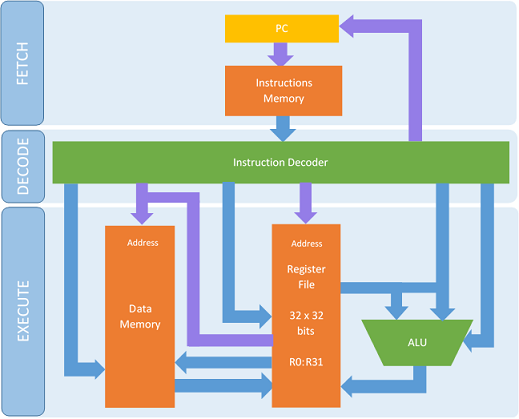

The current pipeline architecture is based on a 3-stages pipeline:

- Fetch

- Decode

- Execute

The following diagram shows the components of the architecture along with the pipeline and the interaction with its components:

| Name | Description |

|---|---|

| R0 | Status Register |

| R1 - R31 | General Purpose |

The status register corresponds to register R0

| Bit | Label | Description |

|---|---|---|

| 0 | -- | Not used |

| 1 | -- | Not used |

| 2 | PF | Parity flag |

| 3 | -- | Not used |

| 4 | -- | Not used |

| 5 | -- | Not used |

| 6 | ZF | Zero flag |

| 7 | SF | Sign flag |

| 8 | -- | Not used |

| 9 | -- | Not used |

| 10 | -- | Not used |

| 11 | OF | Overflow flag |

| 12-31 | -- | Not used |

Human Readable - it is the basic instruction in a assembly file)

| - e.g ADD 14, 18, 14

V

Go Object - the assembly instruction is translated into a

| struct/object to be used by the processor

V

Binary (32-bit) - then it is translated into a 32-bit integer accordignly to formats

| - this instruction will be stored in the instructions memory

V

Go Object - CPU will decode the instruction into an object again and it will

execute the instruction accordignly to the definitions

The next tables shows the format structure of the instructions accordingly to the different types: R, I, J

| Type | Format (32 bits) | |||||

|---|---|---|---|---|---|---|

| R | Opcode (6) | Rd (5) | Rs (5) | Rt (5) | Shmt (5) | Func (6) |

| Type | Format (32 bits) | |||

|---|---|---|---|---|

| I | Opcode (6) | Rd (5) | Rs (5) | - I m m e d i a t e (1 6 b i t s) - |

Type | Format (32 bits)|| -----|------------|----|| J | Opcode (6) | - - - - - - - - - - A d d r e s s (2 6 b i t s ) - - - - - - - - - - |

- All instructions are

32-bitlong (1 word) Rs,Rt, andRdare general purpose registersPCstands for the program counter addressCdenotes a constant (immediate)-denotes that those values do not care

-

From Opcode 000000 to 001111

Syntax | Description | Type | 31 ||||| 0 | Notes | ---------------|----------------|------|--------|----|----|-----|-----|-----|----------------------------| add Rd,Rs,Rt | Rd = Rs + Rt | R | 000000 | Rd | Rs | Rt | - | - | with overflow | addu Rd,Rs,Rt | Rd = Rs + Rt | R | 000001 | Rd | Rs | Rt | - | - | without overflow | sub Rd,Rs,Rt | Rd = Rs - Rt | R | 000010 | Rd | Rs | Rt | - | - | with overflow | subu Rd,Rs,Rt | Rd = Rs - Rt | R | 000011 | Rd | Rs | Rt | - | - | without overflow | addi Rd,Rs,C | Rd = Rs + C | I | 000100 | Rd | Rs | Immediate (16)||| immediate with overflow | addiu Rd,Rs,C | Rd = Rs + C | I | 000101 | Rd | Rs | Immediate (16)||| immediate without overflow | cmp Rd,Rs,Rt | Rd = Rs <=> Rt | R | 000110 | Rd | Rs | Rt | - | - | 1 s<t, 2 =, 4 s>t | mul Rd,Rs,Rt | Rd = Rs * Rt | R | 000111 | Rd | Rs | Rt | - | - | without overflow |

-

From Opcode 010000 to 011111

Syntax | Description | Type | 31 ||||| 0 | Notes | ---------------|----------------|------|--------|----|----|------|-----|-----|-------------------------| lw Rd,Rs,C | Rd = M[Rs + C] | I | 010000 | Rd | Rs | Offset (16) ||| load M[Rs + C] into Rd | sw Rd,Rs,C | M[Rs + C] = Rd | I | 010001 | Rd | Rs | Offset (16) ||| store Rd into M[Rs + C] | lli Rd,C | Rd = C | I | 010010 | Rd | - | Immediate (16) ||| load lower immediate | sli Rd,C | M[Rd] = C | I | 010011 | Rd | - | Immediate (16) ||| store lower immediate | lui Rd,C | Rd = C << 16 | I | 010100 | Rd | - | Immediate (16) ||| load upper immediate | sui Rd,C | M[Rd] = C << 16| I | 010101 | Rd | - | Immediate (16) ||| store upper immediate |

-

From Opcode 100000 to 101111

Syntax | Description | Type | 31 ||||| 0 | Notes | ---------------|-----------------|------|--------|----|----|------|-----|-----|----------------------| beq Rd,Rs,C | br on equal | I | 100000 | Rd | Rs | Immediate (16) ||| PC = PC + 4 + 4C | bne Rd,Rs,C | br on not equal | I | 100001 | Rd | Rs | Immediate (16) ||| PC = PC + 4 + 4C | blt Rd,Rs,C | br on less | I | 100010 | Rd | Rs | Immediate (16) ||| PC = PC + 4 + 4C | bgt Rd,Rs,C | br on greater | I | 100011 | Rd | Rs | Immediate (16) ||| PC = PC + 4 + 4C | j C | jump to C | I | 100100 | C Address (26) ||| PC = 4*C |

This application has a builtin translator that converts human readable assembly instructions into machine code, the available instructions allowed are the ones defined on the previous instructions section.

- Only one instruction allowed per line

- Comments prefix is

; - Comments are allowed to be on a single line or after an instruction in the same line

- It does not care about the amount of empty spaces or tabs

- Branch labels must be on a single line

- No instructions allowed to be on the same line where the branch label is declared

- Blank lines are allowed

; Here are some comments on a new line

PROCESS_LOOP: ; Here is a label followed by an inline comment

ADDI R1, R1, 1 ; Here is a instruction along with its operands and an inline comment

; Here it is an empty line which is allowed followed by an inline comment

ADD R15, R15, R16 ; R15 += C[I]

BLT R1, R20, PROCESS_LOOP ; Here is an instruction using a branch label followed by an inline comment