This code base provides a C++17 framework for field-coupled technology-independent open nanocomputing developed as part of the Munich Nanotech Toolkit (MNT) by the Chair for Design Automation at the Technical University of Munich. Within fiction, algorithms for logic synthesis, placement, routing, clocking, verification, and simulation for Field-coupled Nanocomputing (FCN) technologies are implemented.

To this end, most physical design tasks can be performed on generic data structures that abstract from particular technology or cell design. Using an extensible set of gate libraries, technologies, and cell types, these can easily be compiled down to any desired FCN technology for physical simulation.

For these use cases, fiction provides a C++ header-only library as well as Python bindings that provide data types and algorithms for recurring tasks, e.g., logic network and layout types on different abstraction levels, clocking schemes, gate libraries, design automation algorithms, etc. Additionally, fiction comes with an ABC-like CLI tool that allows quick access to its core functionality.

If you have any questions, feel free to contact us via [email protected] or by creating an issue on GitHub.

Clone the repository and its submodules:

git clone --recursive https://github.com/cda-tum/fiction.gitInside the newly cloned

fictionfolder, trigger the build process:

cmake . -B build

cd build

cmake --build . -j4Run the CLI tool:

cli/fictionHere is an example of running fiction to perform a full physical design flow on a QCA circuit layout that can afterward be simulated in QCADesigner:

Add

fictionas a sub-directory to your CMake project and link againstlibfiction(assuming your project is calledfanfiction):

add_subdirectory(fiction/)

target_link_libraries(fanfiction libfiction)Include the headers you need:

#include <fiction/layouts/cell_level_layout.hpp>

#include <fiction/layouts/clocking_scheme.hpp>

#include <fiction/technology/qca_one_library.hpp>

#include <fiction/io/write_qca_layout.hpp>

#include <fiction/...>Install the Python bindings from PyPI:

pip install mnt.pyfictionImport the bindings:

from mnt import pyfictionFor a full getting started guide, please refer to the documentation.

Physical design in fiction can be performed technology-independent. Only if resulted layouts are to be physically, simulated, a specific technology implementation is required. To this end, fiction supports various potential FCN implementations together with gate libraries to compile gate-level layout abstractions down to the cell level. Additionally, output formats for external physical simulator engines are also supported.

Gate libraries:

File formats:

*.qcafor QCADesigner*.qllfor MagCAD and SCERPA*.fqcafor QCA-STACK*.svgfor visual representation

Many thanks to Frank Sill Torres for his support with the QCADesigner format, to Willem Lambooy for his support with the QCA-STACK format, and to Sophia Kuhn for implementing the SVG writer!

Gate libraries:

File formats:

*.qccfor ToPoliNano*.qllfor ToPoliNano & MagCAD

Many thanks to Umberto Garlando, Fabrizio Riente, and Giuliana Beretta for their support!

Gate libraries:

File formats:

*.sqdfor SiQAD

Many thanks to Samuel Sze Hang Ng for his support!

The fiction framework provides implementations of state-of-the-art design automation algorithms for FCN technologies. These algorithms can be used in evaluation scripts to perform logic synthesis, physical design, layout verification, and physical simulation.

For logic synthesis, fiction relies on the mockturtle library that offers a multitude of logic network types and optimization algorithms. Logic synthesis can be performed in external tools and resulting Verilog/AIGER/BLIF/... files can be parsed by fiction. Alternatively, since mockturtle is included in fiction, synthesis can be applied in the same evaluation script.

For automatic FCN layout obtainment, fiction provides algorithms that receive mockturtle logic networks as input specification and output placed, routed, and clocked generic FCN circuits.

Among these algorithms are

- SMT-based exact placement and routing

- OGD-based scalable placement and routing

- SAT-based one-pass synthesis

- SAT-based multi-path routing

plus several path-finding algorithms that work on generic layouts:

- shortest path via the A* algorithm

- k shortest paths via Yen's algorithm

On top, there is a hexagonalization algorithm to transform Cartesian layouts suitable for QCA into hexagonal layouts suitable for SiDBs, and multiple algorithms to optimize gate-level layouts post-placement:

Layout correctness can be validated using

- Design Rule Violation (DRV) checking

- SAT-based formal verification (equivalence checking)

When a layout is compiled to the cell level via the application of a technology-dependent gate library, it can be simulated using a physical model. Currently, the following simulation algorithms are implemented in fiction:

- Silicon Dangling Bonds (SiDBs)

- Electrostatic Ground State Simulation

- Critical Temperature Simulation

- Operational Domain Computation

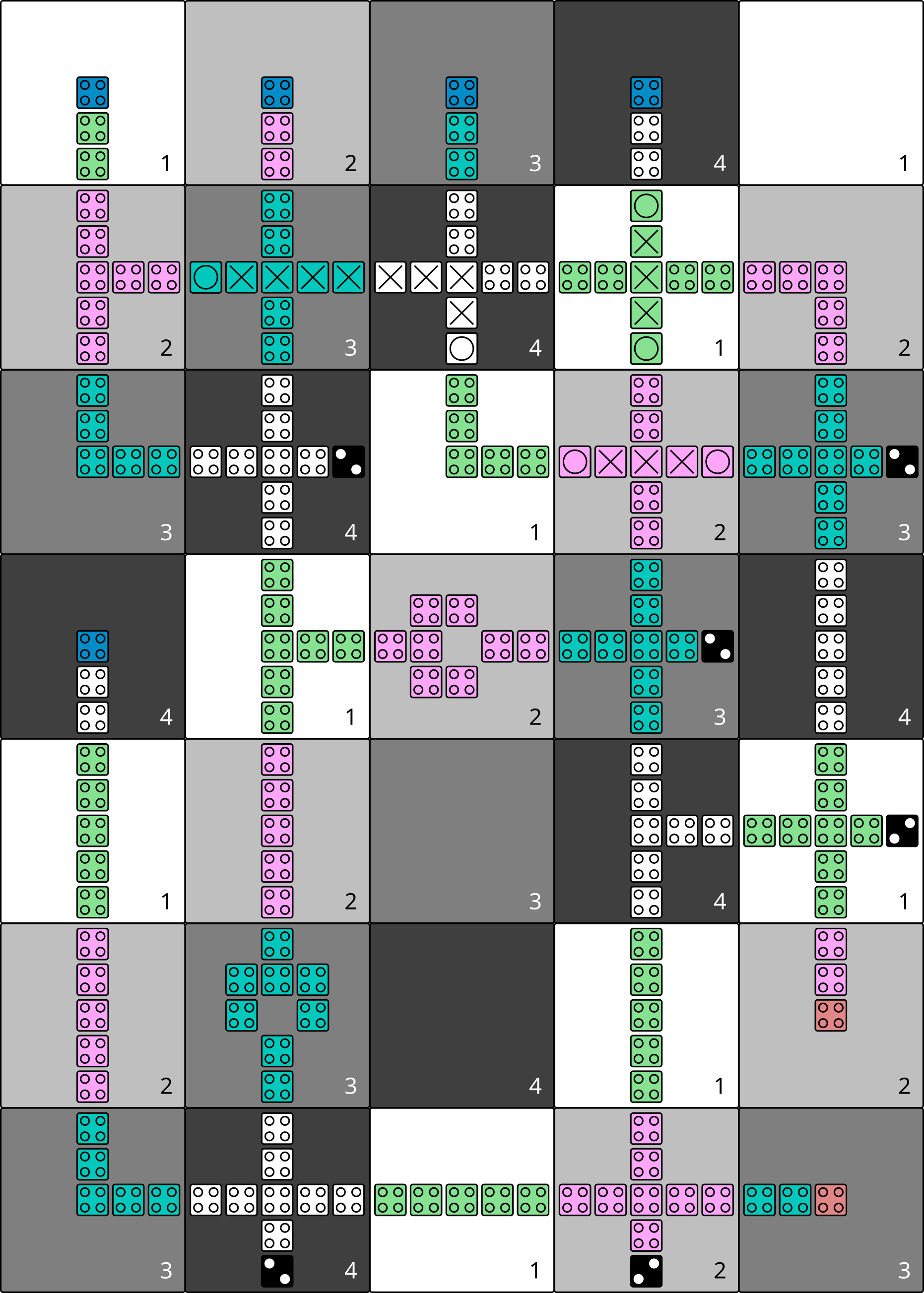

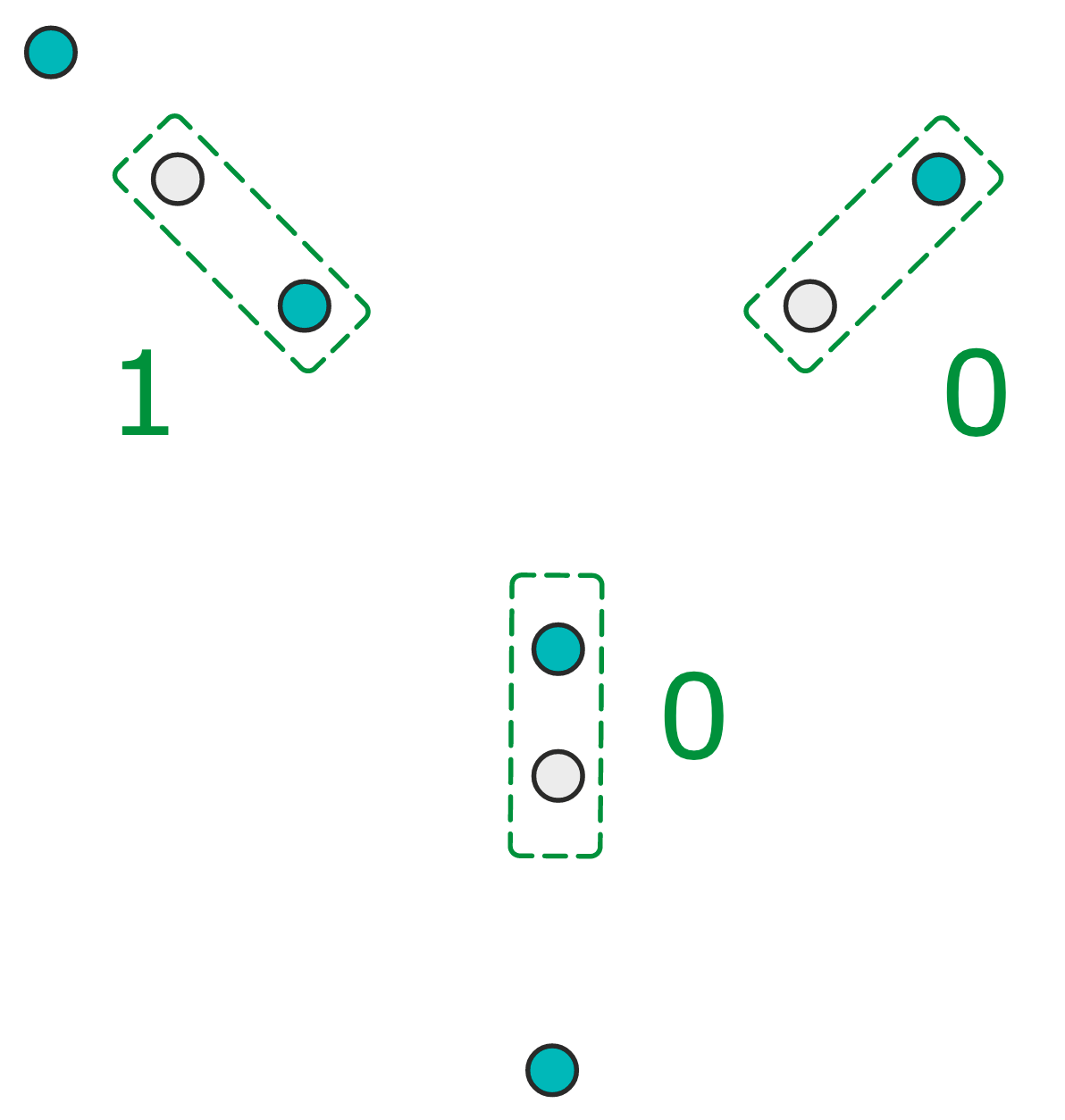

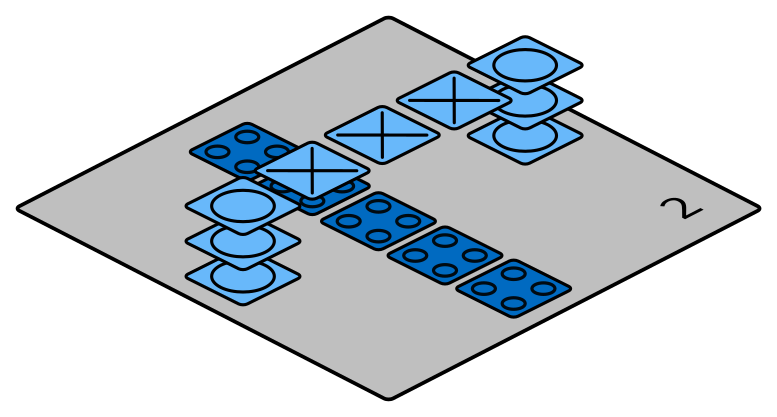

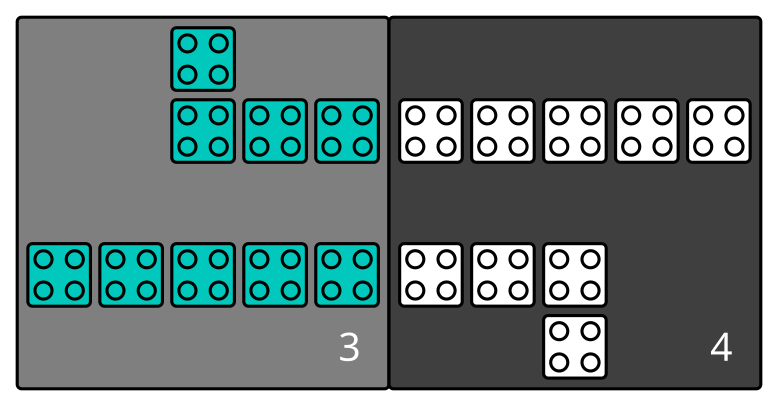

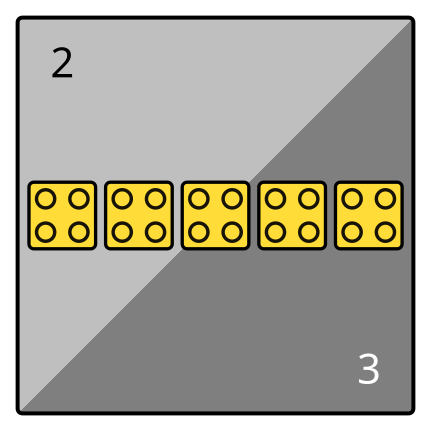

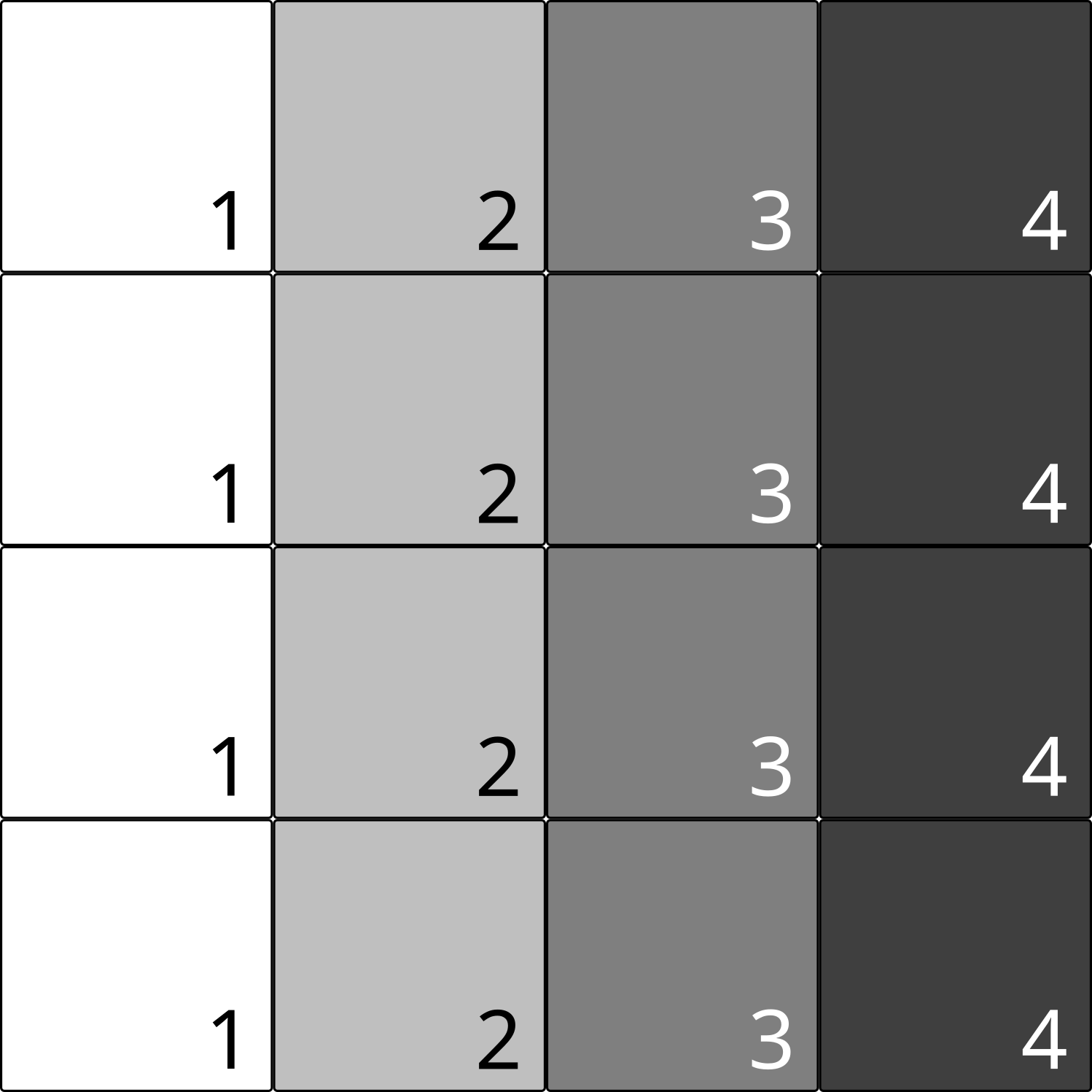

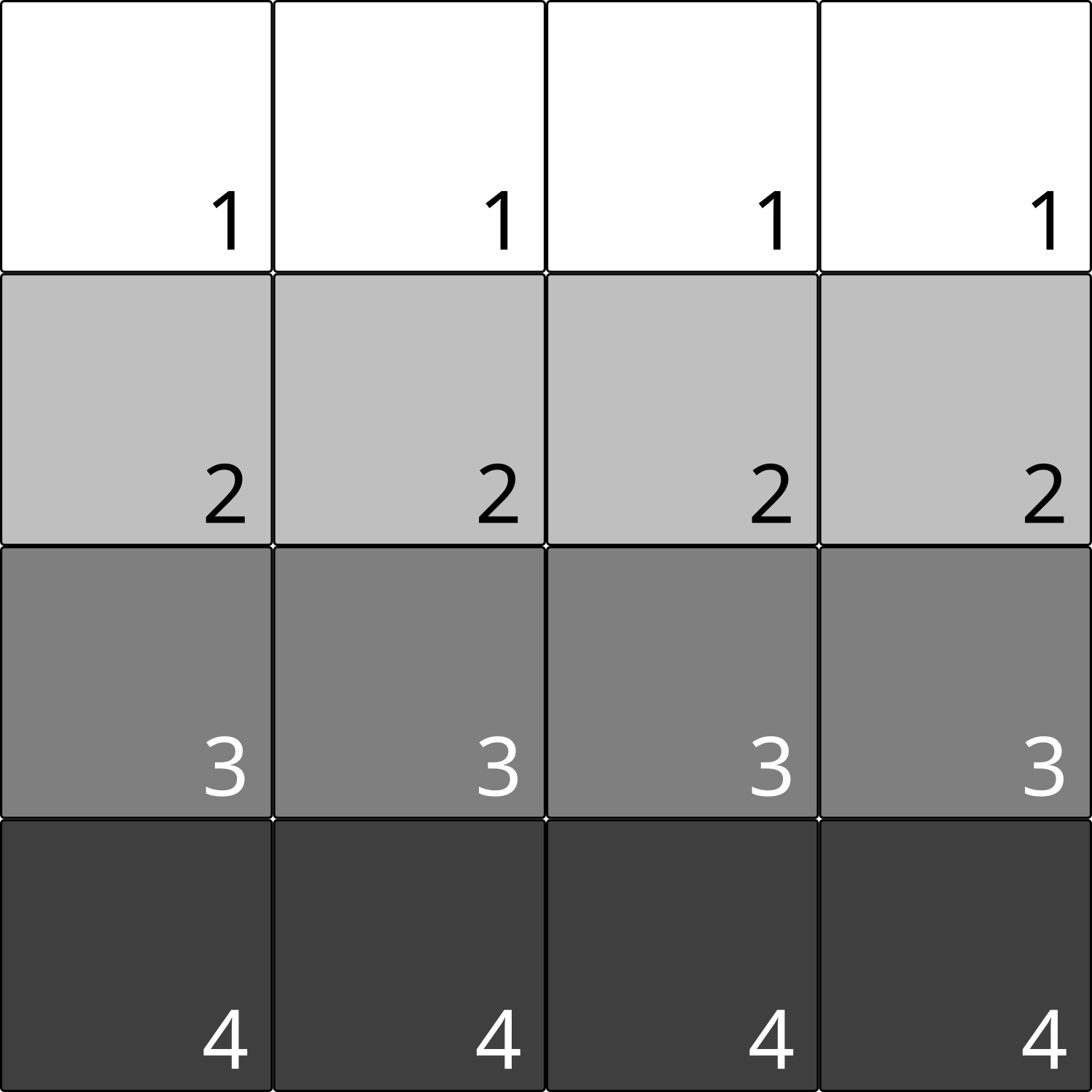

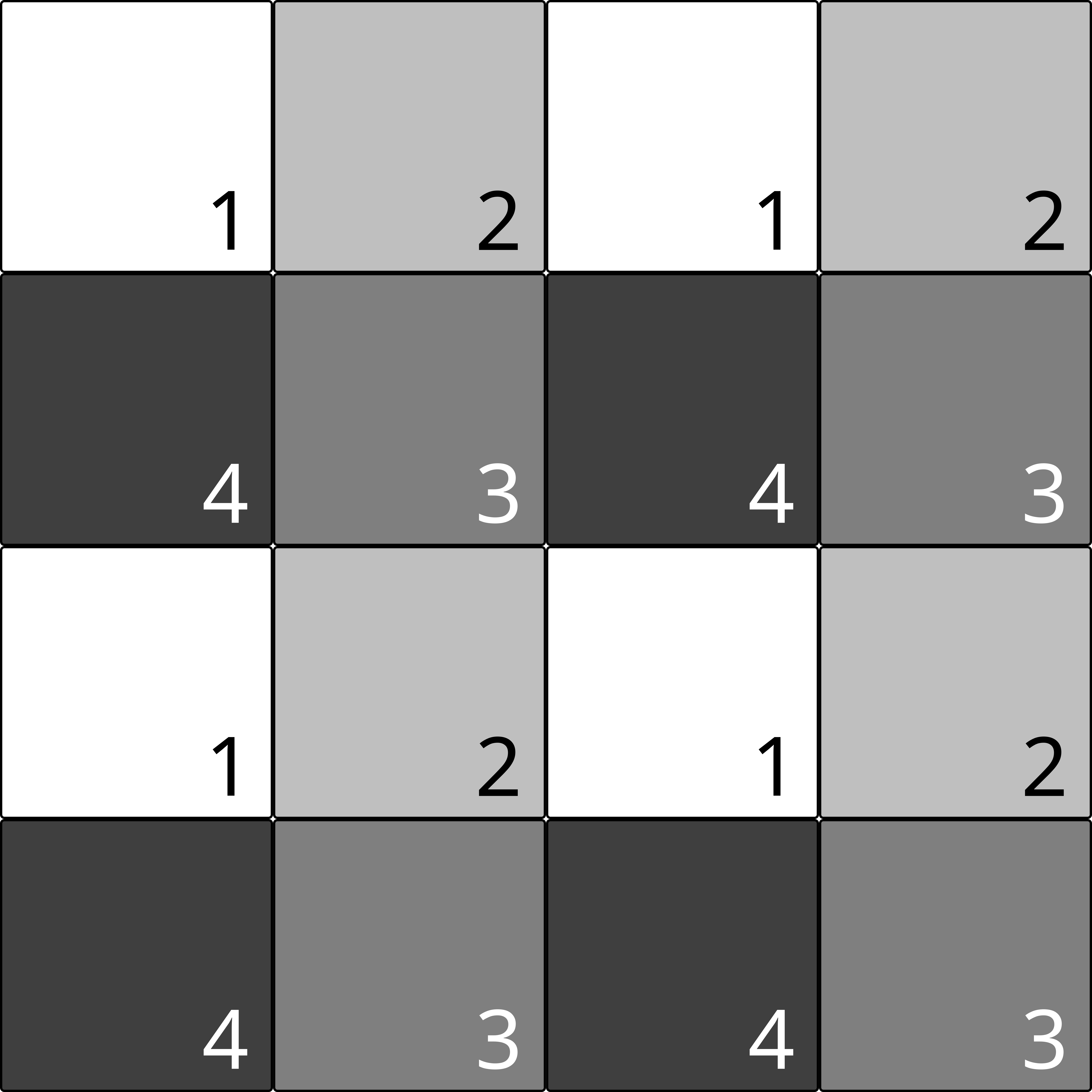

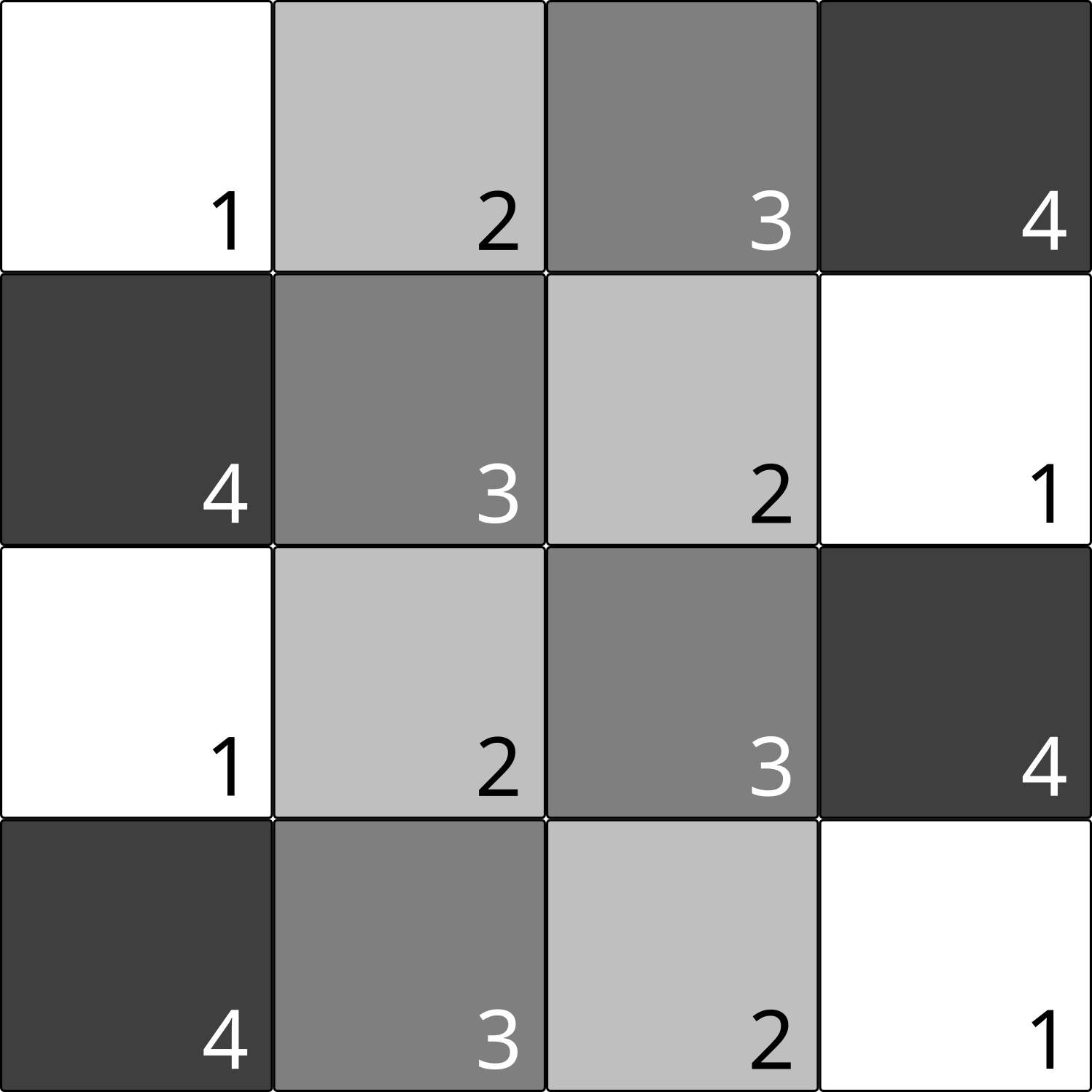

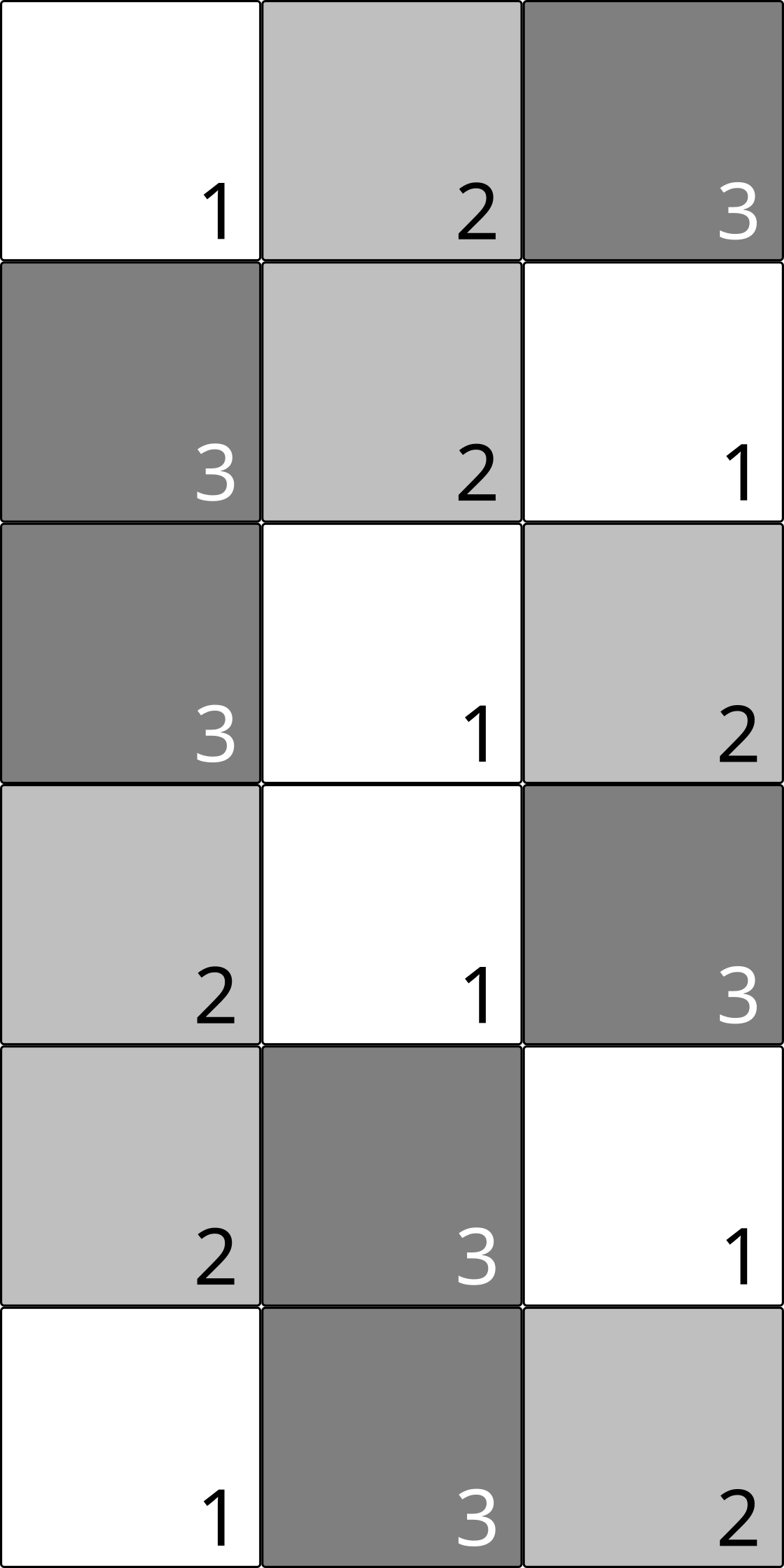

Regular clocking schemes have been proposed in the FCN literature, which can be used as a floor plans for physical design. However, sometimes it can make sense to have more freedom and assign clock numbers on the fly. That is why fiction supports both regular and irregular clocking schemes with variable amounts of clock numbers as QCA for instance uses four clock phases but iNML needs only three.

Built-in schemes are

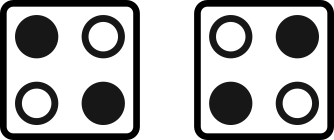

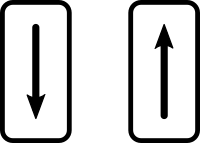

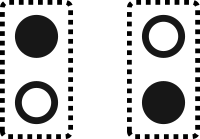

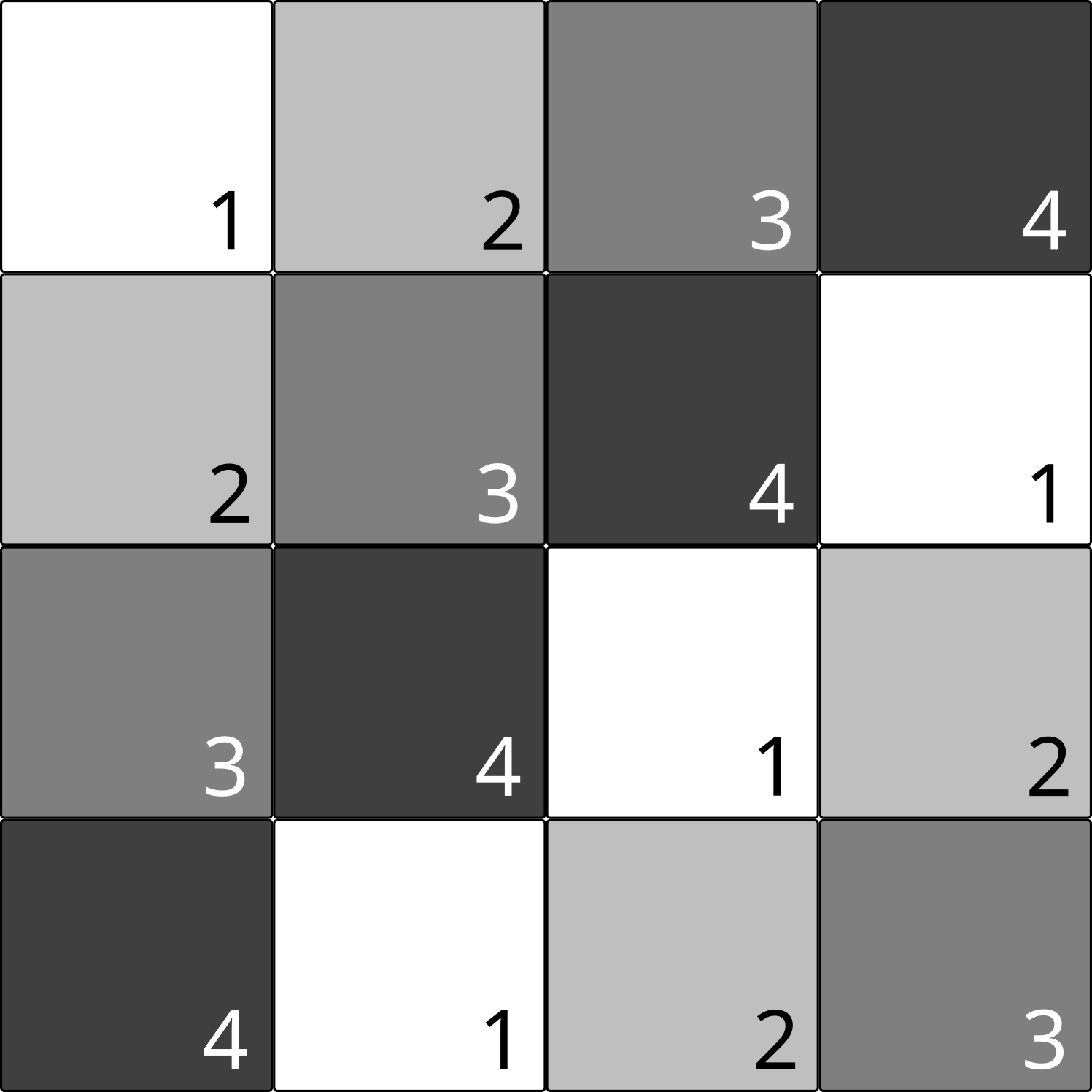

| Columnar | Row | 2DDWave |

|---|---|---|

|

|

|

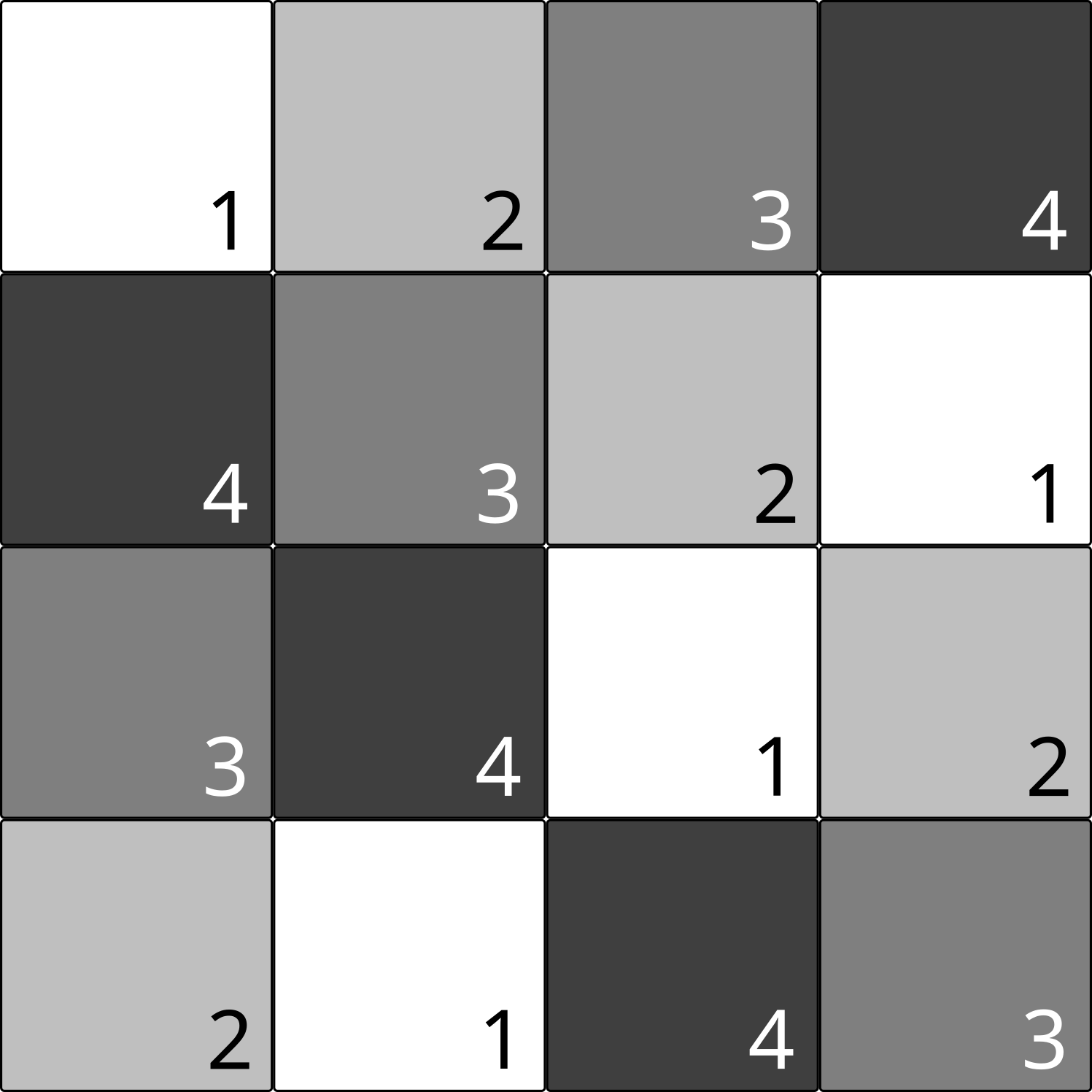

| USE | RES | ESR |

|---|---|---|

|

|

|

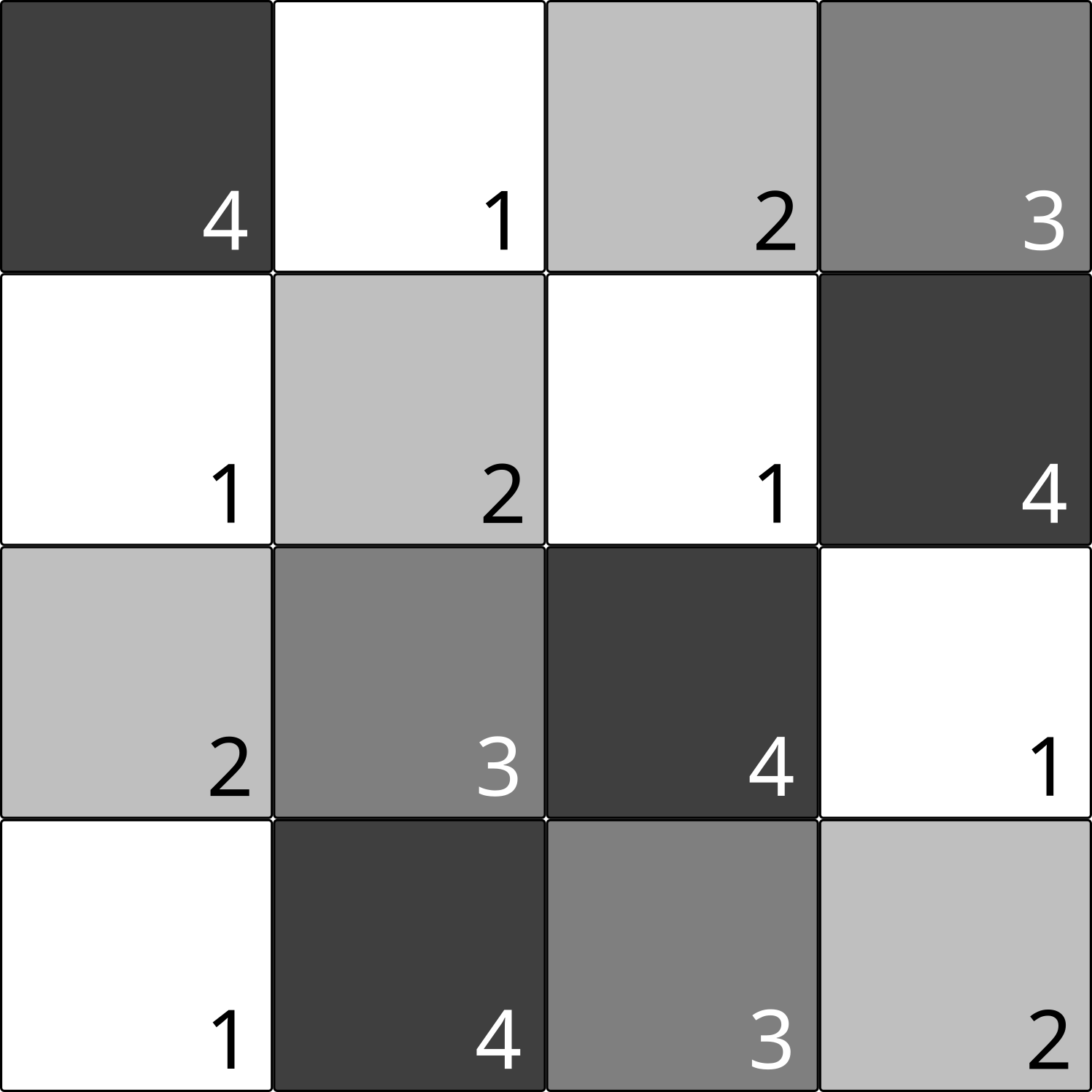

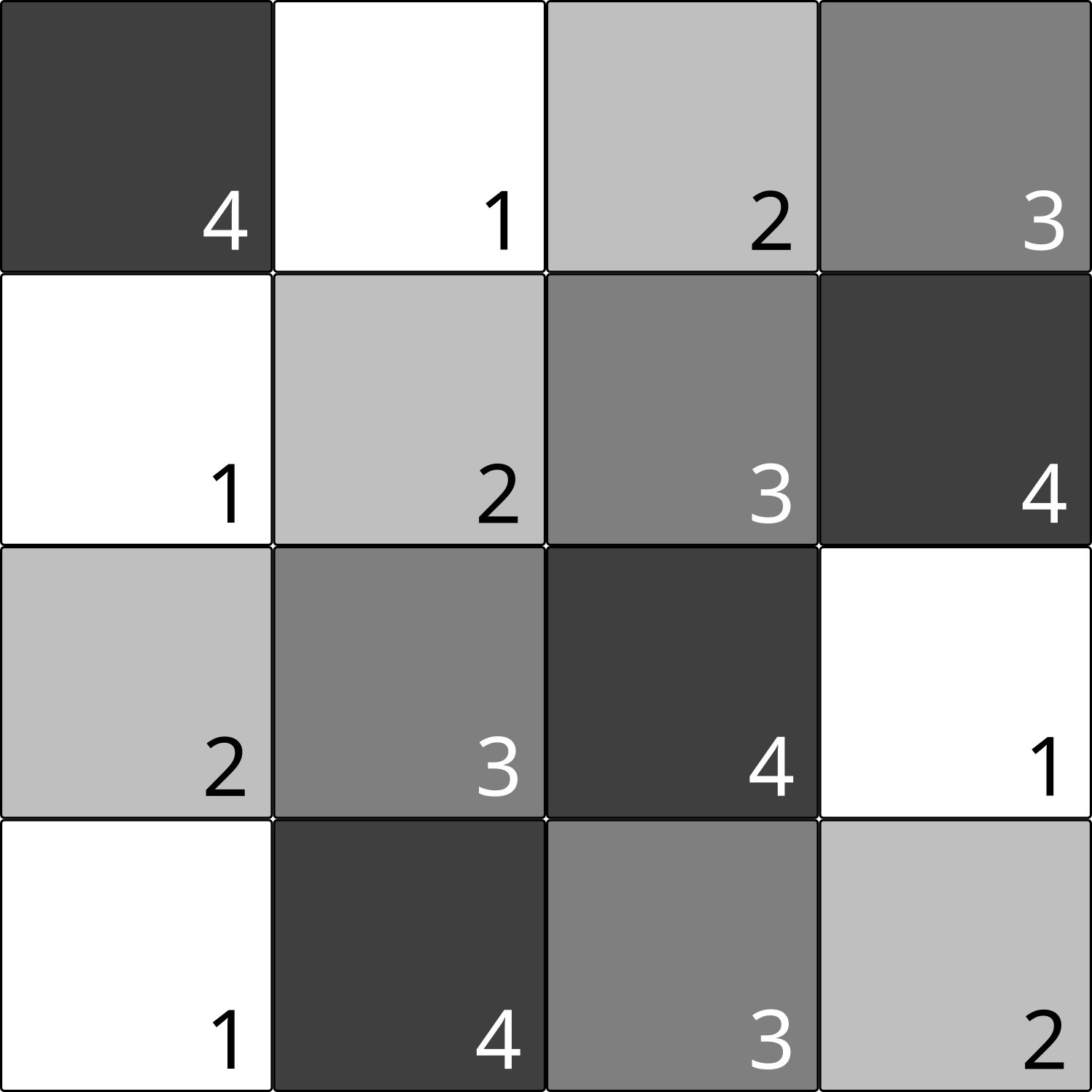

| CFE | Ripple | BANCS |

|---|---|---|

|

|

|

plus the mentioned irregular open clocking that works via a clock map instead of a regular extrapolated cutout.

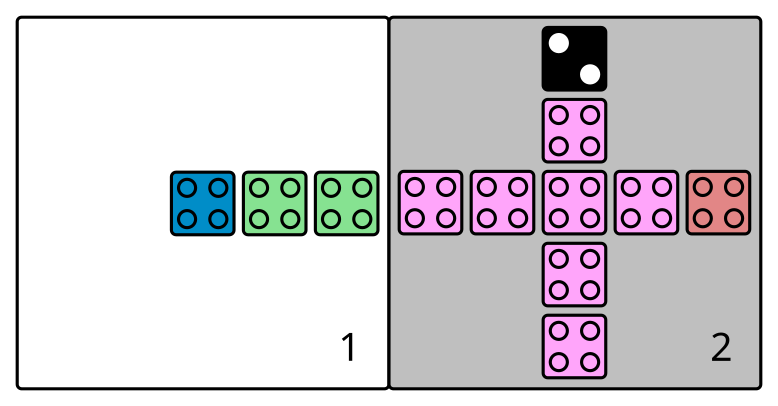

With many FCN technologies considered planar, wire crossings should be minimized if possible. However, there are some options in QCA where, using a second layer, crossings over short distances and co-planar rotated cells become possible. As both are just technical implementations of the same concept, fiction supports crossings as wires in a second grid layer in its data structures for all FCN technologies. They will also be represented as such in corresponding SVG and QCADesigner output. However, note that it is to be interpreted as the concept of crossings and could also be realized co-planar.

Wires are only allowed to cross other wires! Wires crossing gates is considered to lead to unstable signals.

In the literature, both are seen: having input cells (pins) directly located in the gate structure or using designated I/O elements that are located outside of gates. This distinction only makes sense on the gate level and fiction supports both approaches and offers usage in the implemented physical design algorithms.

Gate-level abstraction has its limits. Often, chip area is wasted when only using a single wire per tile. In fiction, cell-level layouts allow for precise control over cell placement and can, thus, also create multiple wire segments per clock zone. Physical simulation can give an indication of whether the built structures are implementing the intended functionality.

A technology extension proposes to utilize the external clock signal generator in an unconventional way: by creating further asymmetric clock signals with extended Hold phases that are assigned to specific wire tiles, synchronization elements can be created that stall signals over multiple clock cycles. These artificial latches are able to feed information to any other clock number, but their usage reduces the overall throughput of the layout. In return, long wire detours for signal synchronization can be prevented.

Designed layouts can be evaluated with regard to several cost functions. The following metrics are currently implemented:

Gate-level layouts:

- Circuit dimension in tiles

- Number of gate tiles

- Number of wire tiles

- Number of wire crossings

- Number of synchronization elements

- Critical path

- Throughput

- Bounding box

- Energy dissipation based on a physical model (QCA only)

Cell-level layouts:

- Circuit dimension in cells

- Number of cells

- Bounding box

- Area usage in nm²

To objectively evaluate and compare software and design automation

tools, MNT Bench provides gate-level

layouts for various gate libraries and clocking schemes, generated using the latest physical design and

optimization algorithms, with fiction offering the corresponding read and write utilities to generate gate-level

layouts from gate-level layout files (.fgl) and vice versa.

Additionally, the benchmarks folder contains the function

descriptions of frequently used benchmark sets in Verilog format (.v) provided

by MNT Bench.

Since fiction is academic software, we would be thankful if you referred to it by citing the following publication:

@misc{fiction,

author = {Walter, Marcel and Wille, Robert and Sill Torres, Frank and Gro{\ss}e, Daniel and Drechsler, Rolf},

title = {{fiction: An Open Source Framework for the Design of Field-coupled Nanocomputing Circuits}},

archivePrefix = {arXiv},

eprint = {1905.02477},

note = {arXiv:1905.02477},

year = {2019},

month = {May}

}Additionally, many algorithms implemented in fiction have been published individually. For a full list of publications, please refer to the documentation.

The Munich Nanotech Toolkit has been supported by the Bavarian State Ministry for Science and Arts through the Distinguished Professorship Program.